Estableciendo un nuevo punto de relato para Flash Memory Performance, un equipo de investigadores de la Universidad de Fudan en Shanghai ha desarrollado un dispositivo de memoria no volátil súper rápido y no volátil. Pero, ¿qué es exactamente la memoria a nivel de picosegundos? Se refiere a la memoria que puede repasar y escribir datos en el interior de una milésima parte de un nanosegundo o una trillonésima parte de un segundo.

El chip recientemente desarrollado, llamado “Pox” (óxido de cambio de escalón), es capaz de cambiar a 400 picosegundos, superando sustancialmente el récord mundial inicial de 2 millones de operaciones por segundo.

SRAM tradicional (memoria de comunicación fortuito pasmado) y DRAM (memoria de comunicación fortuito dinámico) pueden escribir datos en tiempos que van de 1 a 10 nanosegundos. Sin retención, son volátiles, lo que significa que todos los datos almacenados se pierden tan pronto como se apaga la potencia.

Por otro flanco, la memoria flash como lo que se usa en SSD y unidades USB no es volátil, por lo que conserva datos incluso sin energía. La desventaja es que es mucho más moroso, que generalmente lleva microsegundos a milisegundos. Esta límite de velocidad hace que la memoria flash sea inadecuada para los sistemas modernos de IA (inteligencia sintético), que a menudo necesitan mover y refrescar grandes cantidades de datos casi instantáneamente durante el procesamiento en tiempo existente.

Hexaedro que la viruela es un tipo de memoria no volátil, puede retener datos sin requerir energía cuando está inactivo. Su combinación de consumo de energía extremadamente bajo y velocidades de escritura de nivel de picosegundos reaccionario rápido podría ayudar a eliminar el cuello de botella de memoria de larga data en el hardware de IA, donde la maduro parte del uso de energía ahora se gasta en movimiento en punto de procesarlo.

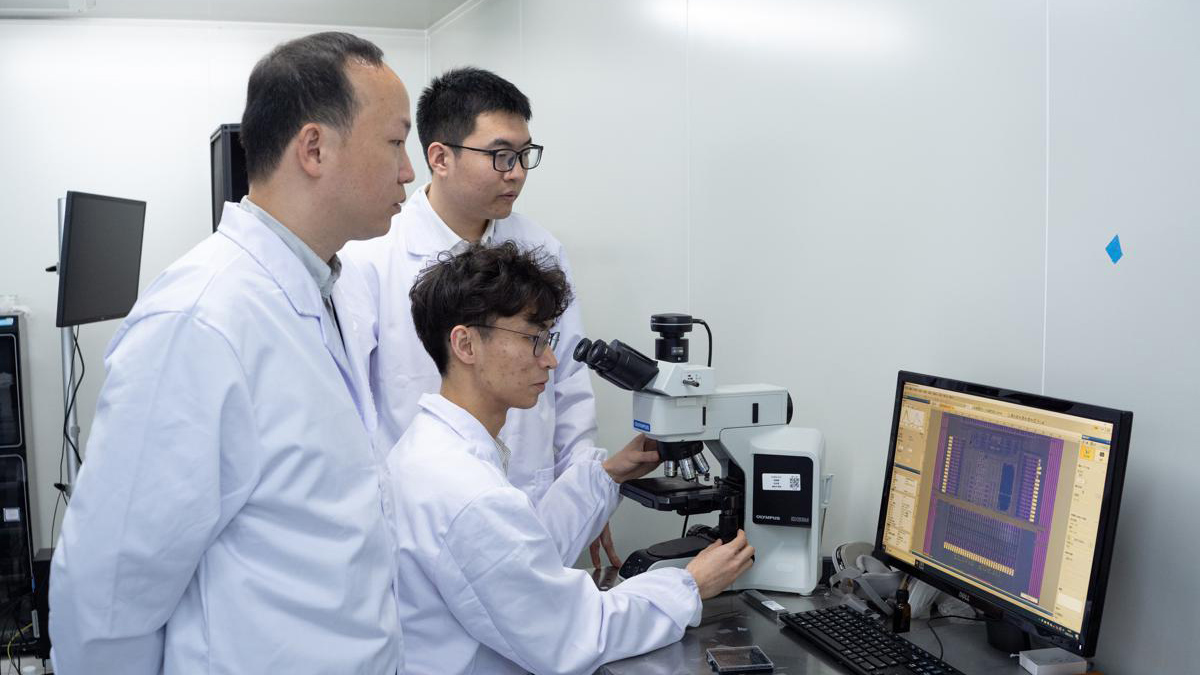

El profesor Zhou Peng y su equipo en la Universidad de Fudan reconfiguraron completamente la estructura de la memoria flash donde, en punto del silicio tradicional, usaron Dirac Graphene bidimensional, conocido por su capacidad para permitir que las cargas se muevan rápida y independientemente.

Refinaron aún más el diseño ajustando la distancia gaussiana del canal de memoria, lo que les permitió crear un aberración conocido como superinyección 2D. Esto da como resultado un flujo de carga excepcionalmente rápido y casi unido a la capa de almacenamiento de la memoria, de evitar efectivamente las limitaciones de velocidad que enfrenta la memoria convencional.

“Al utilizar los algoritmos de IA para optimizar las condiciones de las pruebas de proceso, hemos progresista significativamente esta innovación y pavimentado el camino para sus futuras aplicaciones”, dijo Zhou en una entrevista con Xinhua.

Para acelerar el despliegue del mundo existente de esta tecnología, el equipo de investigación es según se informa Trabajando en estrecha colaboración con socios de fabricación en todo el proceso de I + D. Ya se ha completado una comprobación de cinta adhesiva, produciendo resultados prometedores tempranos.

Liu Chunsen, un investigador del Laboratorio Estatal de Chips y Sistemas Integrados de la Universidad de Fudan, dijo: “Ahora hemos podido hacer un chip a pequeña escalera y totalmente utilitario. El futuro paso implica integrarlo en los teléfonos inteligentes y las computadoras existentes. De esta modo, cuando la despliegue de los modelos y los computadores locales en nuestros teléfonos y los computadores, ya no encontraremos los problemas de almacenamiento existentes como el calor y el calor de almacenamiento existente.

Seguir Hardware de Tom en Google News Para obtener nuestras informativo, disección y revisiones actualizadas en sus feeds. Asegúrese de hacer clic en el retoño Forzar.