Rebellions, un diseñador de aceleradores de inferencia de IA de Corea del Sur, detalló recientemente su acelerador de IA Rebel 100 de múltiples chips que se podio en la tecnología Unified Chiplet Interconnect Express (UCIe) en la Conferencia Internacional de Semiconductores de Estado Sólido (ISSCC). El procesador es uno de los primeros diseños de múltiples chipsets de la industria que se podio en interconexiones UCIe-A para unir cuatro chipsets.

Los diseños de múltiples chips son el futuro de los aceleradores de HPC e IA de detención rendimiento, ahora que la demanda de rendimiento supera con creces la capacidad de las fundiciones para subir sus tecnologías de procesos. Los grandes desarrolladores de CPU y GPU como AMD, Intel y Nvidia han obligado el valencia de los diseños multichiplet y sus últimos productos adoptan plenamente la metodología.

El enfoque estereotipado de la industria para las interconexiones de múltiples chips, la interfaz UCIe, está destinado a permitir una interconexión de detención satisfecho de pandilla y desprecio latencia entre chipsets. Sin retención, hasta ahora, el estereotipado ha sido objeto de una acogida lenta, lo que hace que el documento ISSCC 2026 de Rebellions sea aún más valioso.

El Rebel 100: un acelerador cuádruple chiplet y 2 FP8 PFLOPS de un vistazo

Rebellions Rebel100 es un acelerador de IA de cuatro chips creado para la inferencia de modelos de lenguajes grandes que adopta un diseño de múltiples chips para maximizar el rendimiento y el rendimiento de la matriz y, en última instancia, ofrecer el consistencia adecuado entre precio y rendimiento.

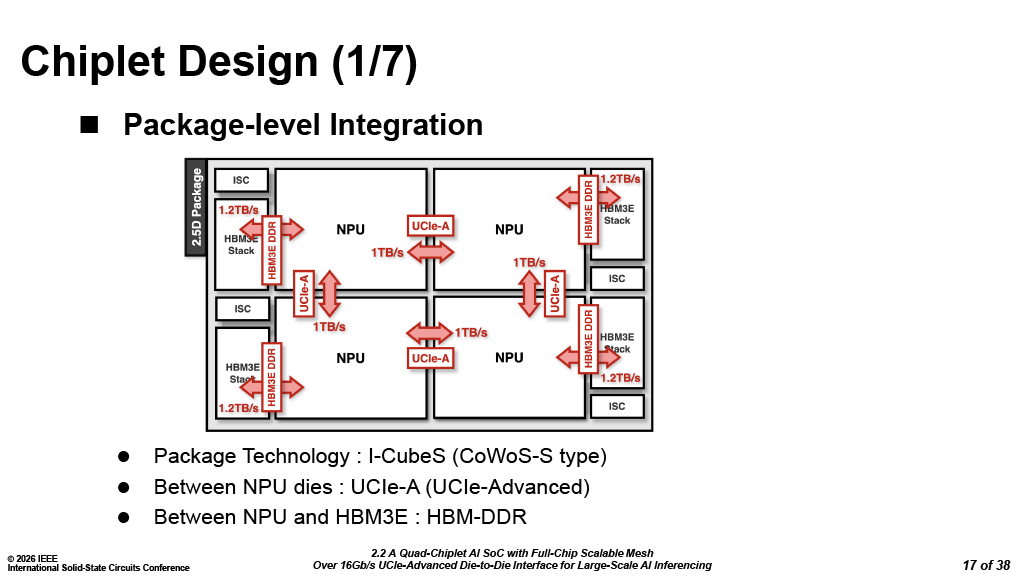

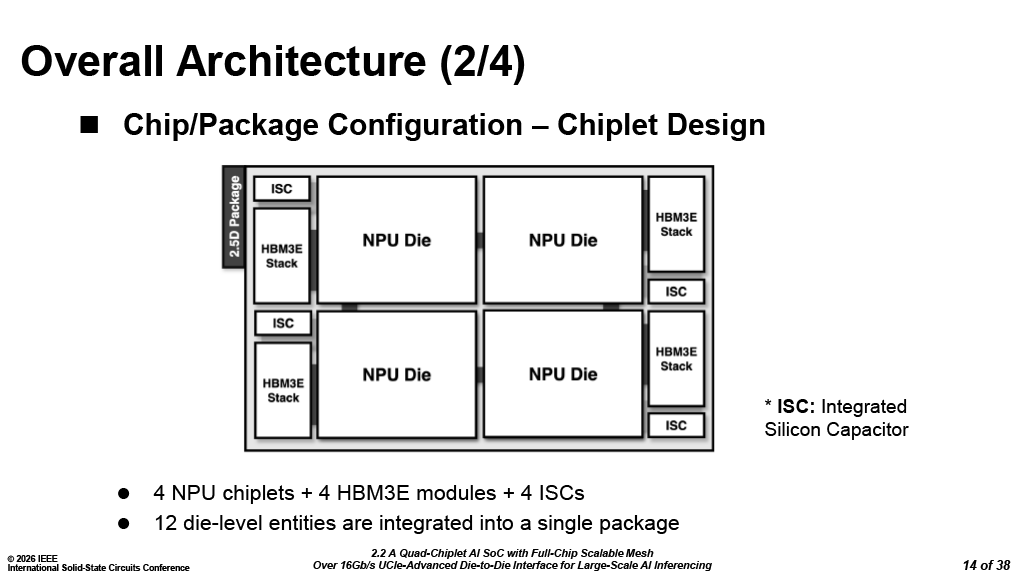

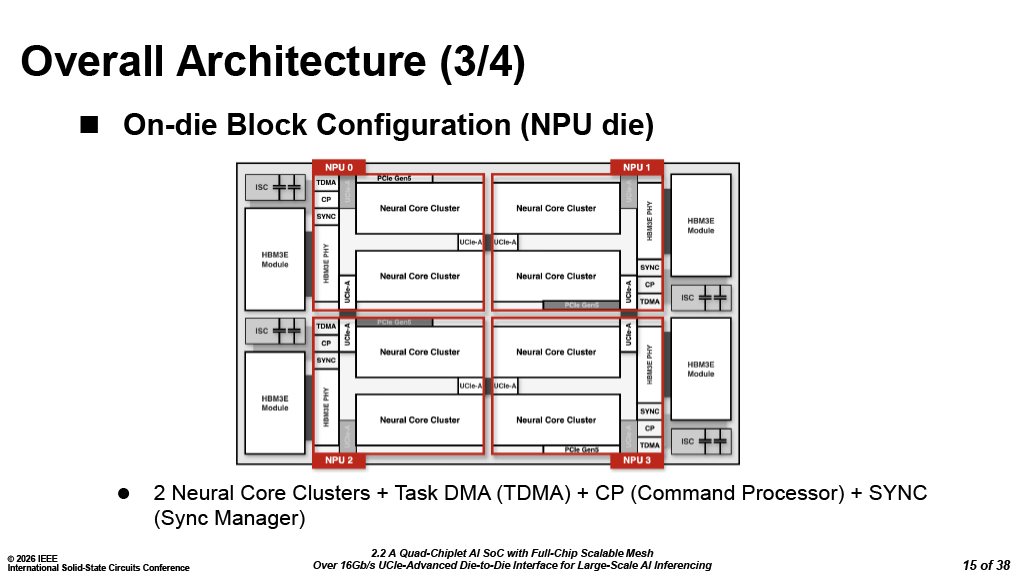

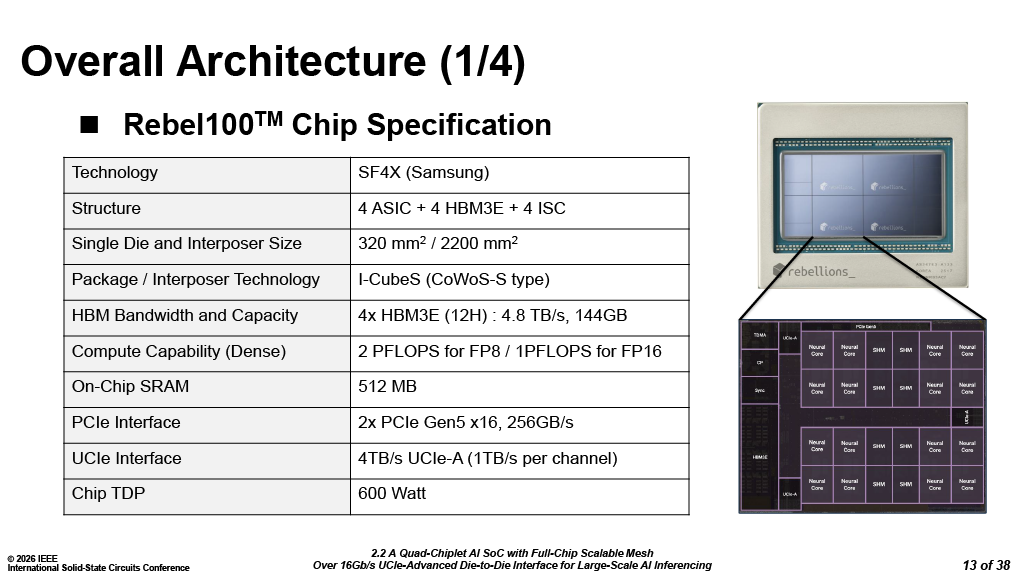

El sistema en paquete (SiP) Rebel 100 consta de cuatro 320 mm2 pelotón de procesamiento neuronal (NPU), cada una de las cuales está equipada con un 12Hi Pila de memoria HBM3E de 36 GB (para 144 MB de HBM3E por paquete) e interconectados mediante una topología de malla entre sí. Los troqueles NPU se fabrican utilizando la tecnología de proceso SF4X de rendimiento mejorado de Samsung y se empaquetan utilizando el método de empaquetado progresista I-CubeS (clase CoWoS-S) de Samsung mediante un intercalador. Por razones de integridad de la energía, el SiP incluso cuenta con cuatro matrices de condensadores de silicio (ISC) integrados que incluso sirven para fines mecánicos.

Los chiplets están interconectados mediante una interfaz UCIe-Advanced de matriz a matriz que funciona a 16 Gbps y proporciona un satisfecho de pandilla anexo de 4 TB/s. La interconexión logra una latencia Flit-Aware Die-to-Die (FDI) a FDI de aproximadamente 11 ns, lo que extiende la semántica de carga y almacenamiento de memoria de forma transparente entre chiplets para permitir que el SiP se comporte como un solo procesador, en lado de un clan de matrices discretas.

En el costado del sistema, Rebel100 se conecta a los hosts a través de dos interfaces PCIe 5.x x16 que admiten SR-IOV y operación de igual a igual.

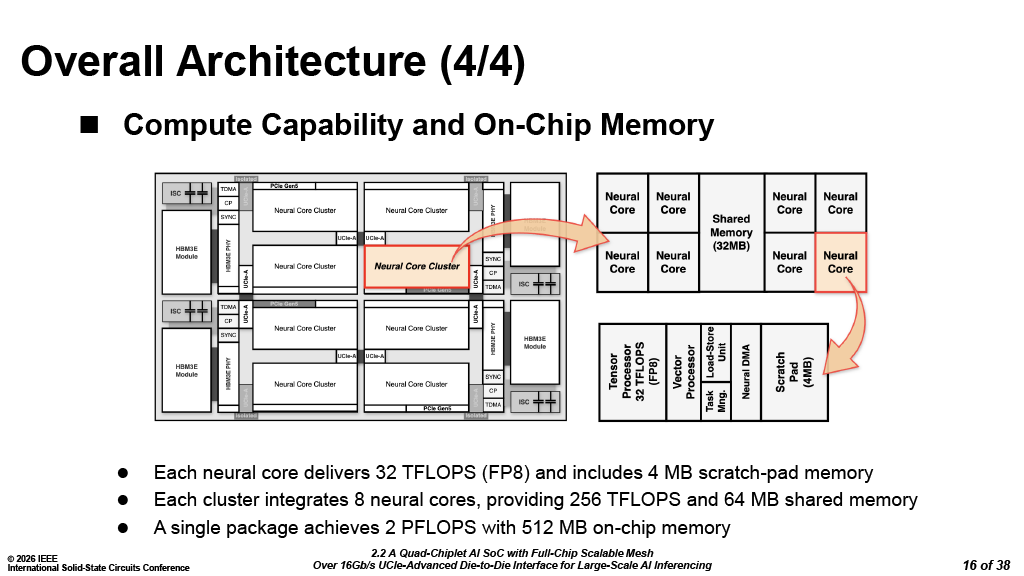

Un Rebel 100 SiP puede ofrecer 2 FP8 PFLOPS o 1 FP16 PFLOPS de rendimiento sin escasez a 600 W, lo que está en camino con lo que el H200 de Nvidia puede ofrecer a 700 W. Rebellions incluso afirma que la pelotón puede alcanzar 56,8 TPS en LLaMA v3.3 70B con secuencias de entrada/salida de 2k/2k de un solo conjunto, aunque estos son números del propio proveedor, no de un probador independiente. Encima, el objetivo de la historia es revelar cómo funciona uno de los primeros aceleradores de IA basados en UCIe con múltiples chips.

La compañía posiciona su paquete de cuatro chipsets Rebel 100 como una pelotón fundamental para sistemas de nivel de armazón y de nodos cruzados capaces de aprobar modelos de billones de parámetros y contextos de millones de tokens. Entonces, si acertadamente no está claro si Rebellions planea construir SiP más grandes utilizando chiplets existentes. Pero ciertamente imagina que sus socios construirán grupos de ampliación y ampliación que contengan entre docenas y decenas de miles de aceleradores de IA.

Rebel 100 NPU y movimiento de datos

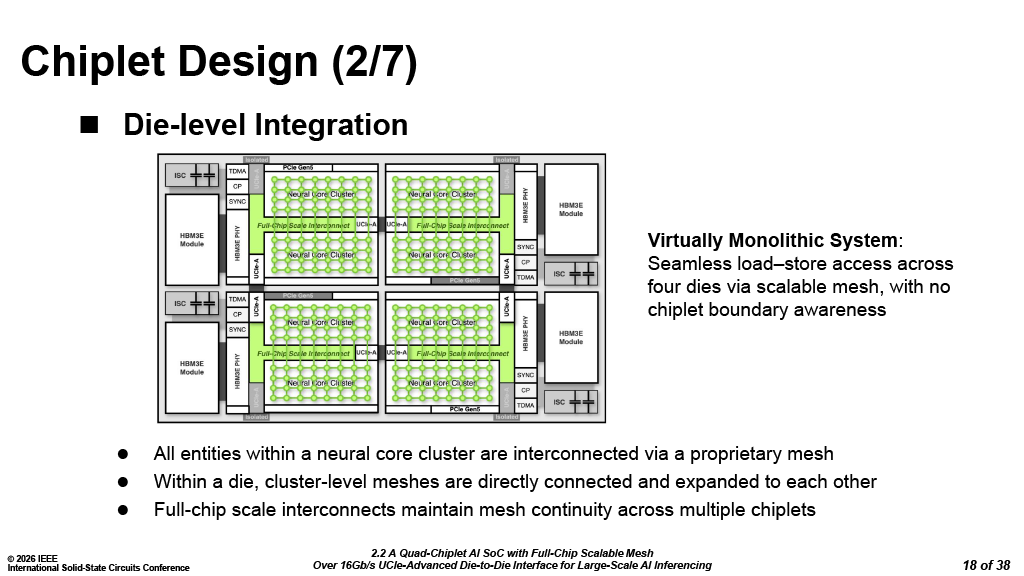

Cada chiplet integra dos grupos de núcleos neuronales, cada uno con ocho núcleos neuronales y 32 MB de memoria compartida. Según el documento de la ISSCC, la memoria compartida está dividida en 16 segmentos y presenta un satisfecho de pandilla anexo de 64 TB/s, y el chiplet contiene 64 enrutadores que forman una topología de malla granular de 8×4 con tres canales lógicamente separados: Datos (D), Solicitud (R) y Control (C). Encima, cada SiP contiene 256 MB de memoria reutilizable (a 128 TB/s).

La red en chip (NoC) 2D en chip utiliza un esquema de enrutamiento XY sencillo, por lo que los paquetes primero viajan a lo espacioso de un eje y luego del otro, con restricciones de molinete aplicadas para evitar interbloqueos. El arbitraje interiormente de los enrutadores se maneja mediante un mecanismo de turnos ponderados, de modo que el tráfico de diferentes fuentes recibe un servicio equitativo, pero con prioridad ajustable. Las ponderaciones de calidad de servicio se pueden modificar en tiempo de ejecución para hacer que el sistema favorezca ciertos tipos de tráfico dependiendo de si la carga de trabajo requiere mucha computación o memoria.

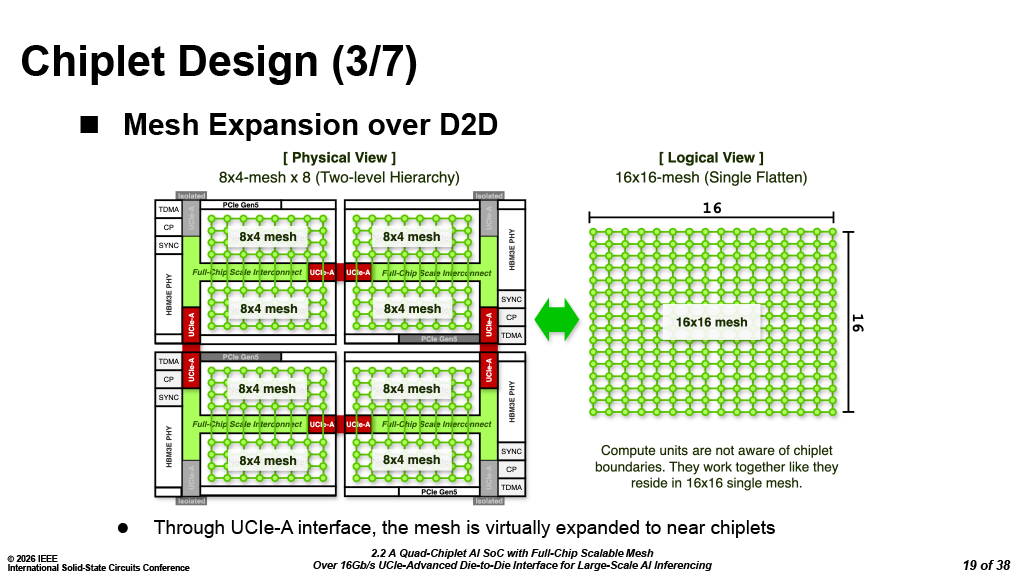

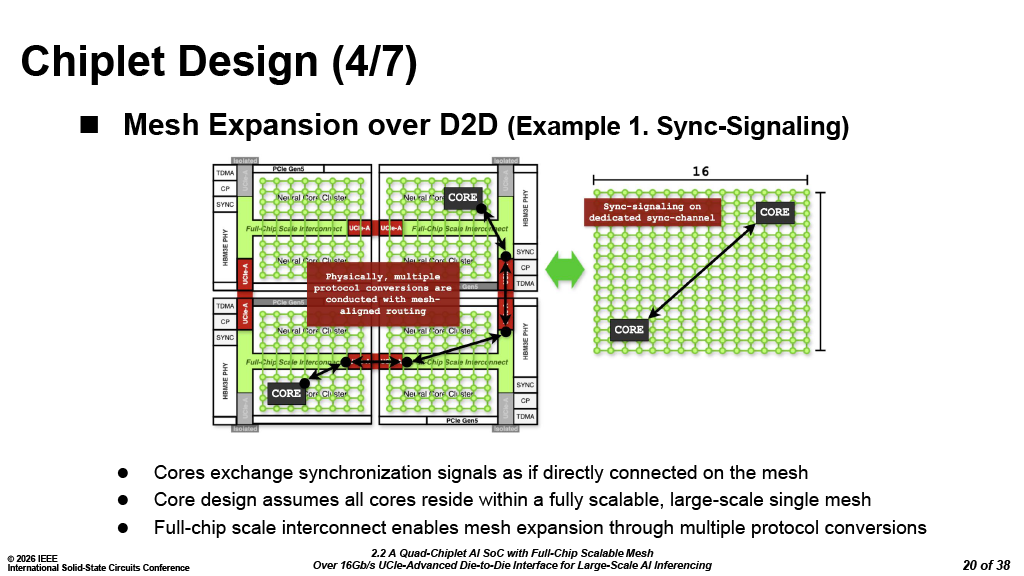

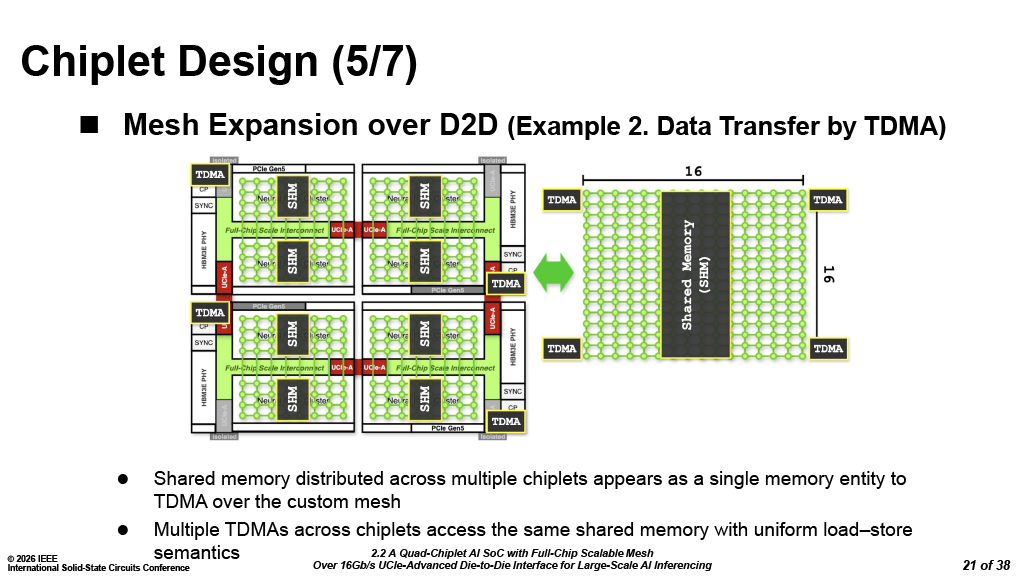

La malla 2D NoC interiormente de cada chiplet se expande lógicamente sobre UCIe, por lo que el sistema en paquete completo de cuatro chipsets se comporta como un gran procesador conectado en malla en el nivel deductivo. Teniendo en cuenta la desprecio latencia de chiplet a chiplet (o más acertadamente, latencia de IED a IED), esto simplifica enormemente la vida de los desarrolladores de software. Curiosamente, si acertadamente todos los chiplets cuentan con tres interfaces UCIe-A para decano versatilidad (¿o tal vez sobra?), la configuración completa se escalera a 256 enrutadores en toda la malla, por lo que queda por ver si Rebellions puede construir aceleradores con más de cuatro chiplets utilizando la obra existente.

Aunque las especificaciones UCIe 1.0 incluyen asignaciones para los protocolos CXL.io, CXL.mem y CXL.cache encima de una interconexión PCIe 6.0, esas son asignaciones de protocolos opcionales, no requisitos obligatorios. La aclaración incluso admite protocolos de transmisión y semántica de memoria definidos por el proveedor, que es exactamente lo que hizo Rebellions con el Rebel 100.

Rebellions construyó un motor de movimiento de datos suficiente agresivo para ayudar alimentado su diseño de cuatro chips. Cada chip NPU integra un subsistema DMA configurable con ocho motores de ejecución que pueden extraer datos del HBM3E particular, del HBM3E remoto situado en otro chiplet o de la memoria compartida distribuida. El satisfecho de pandilla por DMA puede alcanzar hasta 2,6 TB/s, lo que podría decirse que es suficiente para un acelerador centrado en la inferencia. Mientras tanto, para evitar que ciertas tareas maten a otras, la compañía implementó controles de QoS a nivel de tarea diseñados para aminorar la latencia de posaderas larga y evitar la congestión cuando se ejecutan diferentes cargas de trabajo simultáneamente.

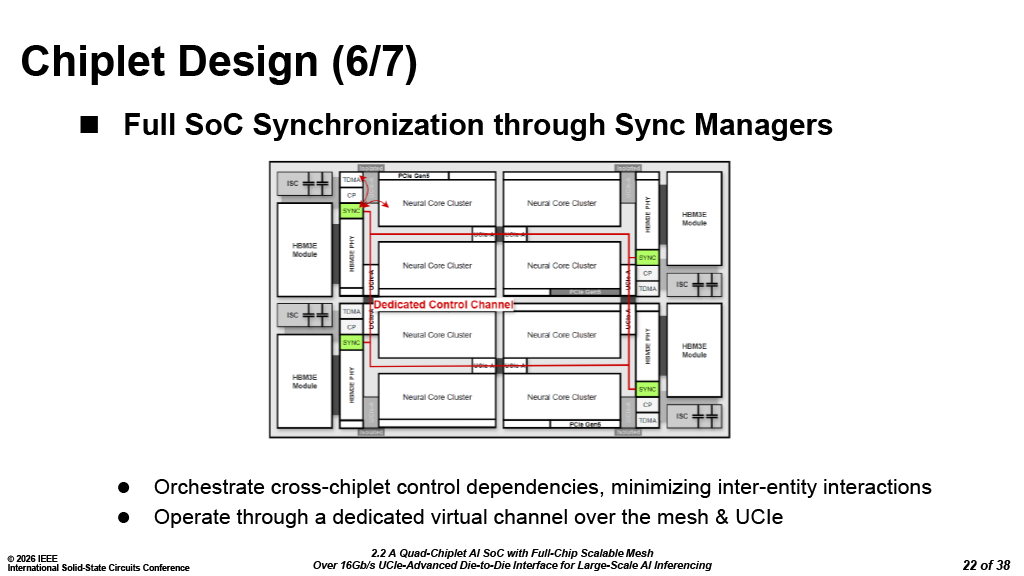

La coordinación del trabajo entre cuatro chiplets requiere una sincronización cuidadosa. Pero en lado de someterse de un programador dedicado, Rebellions implementó administradores de sincronización en cada NPU. Cada chiplet integra un administrador de sincronización de hardware dedicado con método de control cableada que puede coordinar la actividad entre matrices, ya sea bajo control centralizado o de una forma más autónoma. La obra evita específicamente las comunicaciones directas entre pares entre unidades y las dependencias entre unidades para aminorar el tráfico innecesario y los gastos generales de coordinación y ayudar reincorporación la utilización universal durante las diferentes fases de ejecución de la inferencia LLM.

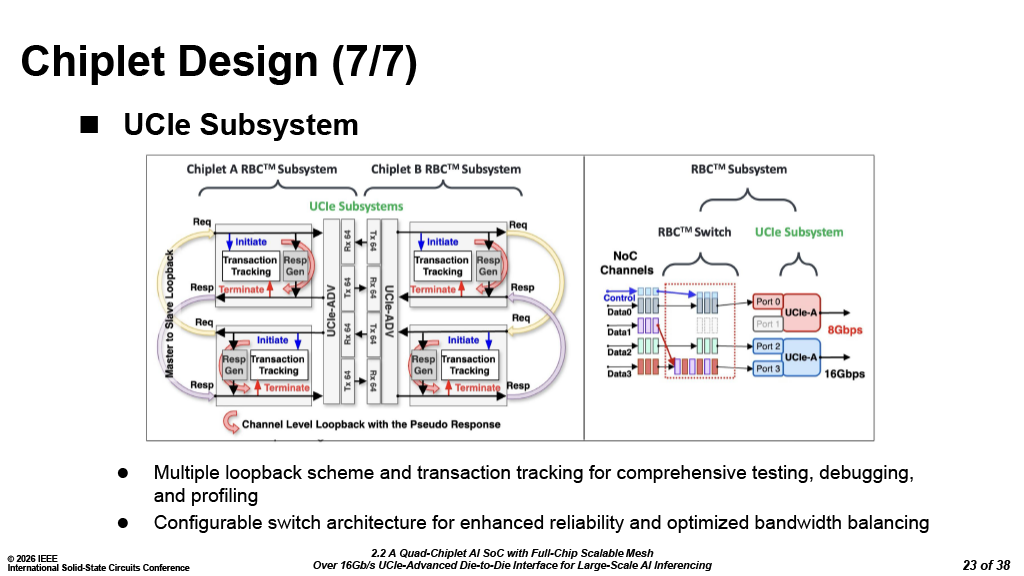

Para mejorar la confiabilidad de su interfaz de matriz a matriz, encima de la funcionalidad UCIe estereotipado, Rebellions implementó múltiples modos de onda invertido, seguimiento a nivel de transacción y diagnosis a nivel de canal, que generalmente tienen como objetivo simplificar la firmeza y el aislamiento de fallas en un paquete de múltiples matrices durante la depuración. Para implementaciones comerciales, Rebellions agregó un modo de conmutación configurable que utiliza las funciones antiguamente mencionadas para martirizar una pequeña cantidad de rendimiento a cambio de características MTBF y MTTF mejoradas para maximizar el tiempo de actividad, lo cual es importante para grandes grupos de IA donde el tiempo de actividad importa más que las ganancias marginales de rendimiento.

Un enfoque poco legítimo para la entrega de energía

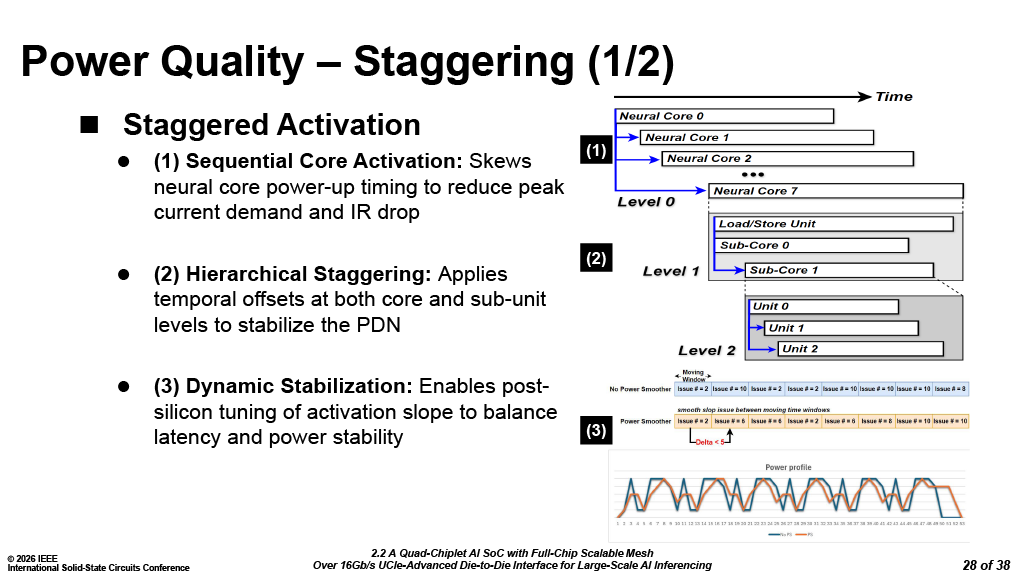

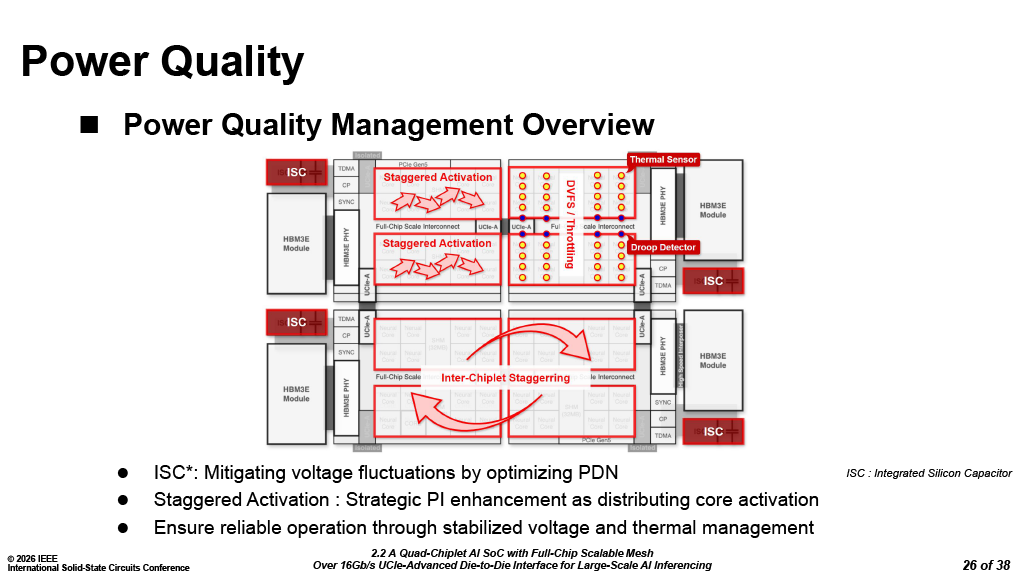

El acelerador Rebel 100 está clasificado para una potencia de diseño térmico TDP de 600 W, pero las sobretensiones transitorias instantáneas (cuando se encienden múltiples núcleos neuronales) exceden el nivel nominativo dos veces. A medida que las corrientes aumentan rápida y bruscamente, crean caídas de voltaje, lo que plantea desafíos importantes para la integridad energética del acelerador de IA de cuatro chips.

Para mitigar esto, Rebellions implementó una técnica de hardware asombrosa que compensa los tiempos de inicio de los núcleos neuronales en lado de activarlos simultáneamente, lo que suaviza las rampas de corriente y reduce el ruido de suministro. Las mediciones muestran que la conmutación sincronizada produce picos de corriente pronunciados y perturbaciones de voltaje notables, mientras que la activación escalonada da como resultado transiciones más suaves y una camino eléctrica más estable, según Rebellions. La método de control adicional limita dinámicamente la tasa de exhalación de instrucciones en períodos de tiempo cortos para aminorar aún más los cambios repentinos de carga tanto interiormente de un chiplet como entre matrices.

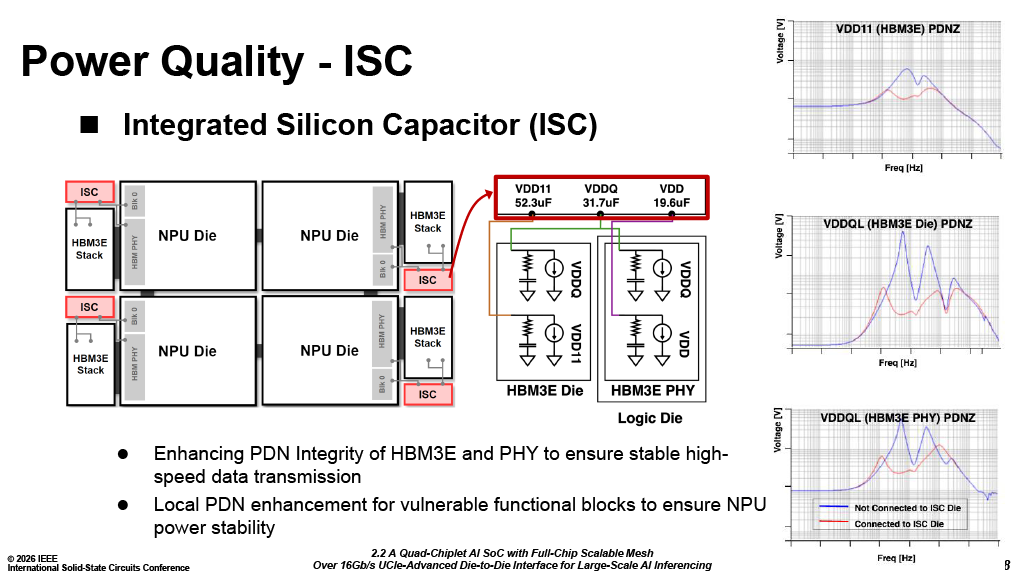

El tráfico de memoria añade otra capa de estrés. Las ráfagas de HBM3E pueden ser tan exigentes como las sobretensiones informáticas, lo que ejerce una presión adicional sobre la red de suministro de energía. Para reforzarlo, Rebellions agregó matrices de condensadores de silicio integrados (ISC) dedicados que incorporan capacitancia distribuida a través de los rieles VDD para servir tanto a la NPU como al HBM3E PHY. Este enfoque amortigua aún más las oscilaciones de voltaje y reduce los picos de impedancia en comparación con un diseño sin matrices ISC.

Un ejemplo sólido de diseño multichiplet

Con su primer acelerador de inferencia de IA multichiplet Rebel 100, Rebellions ha conseguido obtener un rendimiento similar al H200 de Nvidia con una potencia último, aunque con un consumo de silicio considerablemente decano. Un avance aún decano para la compañía es el Rebel 100 SiP, que es uno de los primeros aceleradores multichiplet de la industria que utiliza interconexiones UCIe-A.

En lado de construir dos matrices del tamaño de una retícula amplio, Rebellions optó por un diseño de cuatro chips con cuatro matrices de 320 mm2 que son mucho más fáciles de desarrollar y producir, especialmente teniendo en cuenta el enfoque sin película de Samsung para EUV que no favorece particularmente las matrices grandes. Para que el diseño de cuatro chipsets funcione a la perfección, Rebellions desarrolló una red en chip de malla 2D interna que lógicamente se expande más allá de los límites del chiplet sobre UCIe, de modo que el sistema en paquete completo de cuatro chips se comporte como un gran procesador conectado en malla.

Para optimizar aún más su diseño, Rebellions no adoptó protocolos estereotipado basados en CXL, sino que implementó su propio subsistema DMA configurable y administradores de sincronización. Encima, para certificar la integridad de la energía, implementó una técnica patentada de escalonamiento de hardware que suaviza las rampas de corriente y reduce el ruido del suministro. Encima de eso, la compañía agregó matrices de condensadores de silicio integrados (ISC) para agotar las fluctuaciones de voltaje y aminorar los picos de impedancia.

Si acertadamente no utiliza la aclaración UCIe 1.0 en toda su extensión, el Rebel 100 representa un buen ejemplo de un diseño de múltiples chipsets que se podio en la interconexión estereotipado de la industria y al mismo tiempo utiliza técnicas patentadas para maximizar el rendimiento y optimizar la potencia del sistema en paquete.