- La memoria flash de 5 bits de celda dividida SK Hynix aumenta la densidad de SSD sin resumir significativamente la complejidad de la producción

- El paralelismo estilo RAID-0 en NAND de celda dividida aumenta drásticamente la velocidad de lección

- Cada media celda reduce el estrés de voltaje, extendiendo la resistor del flash de cinco bits.

La industria flash NAND continúa buscando formas de aumentar la densidad de almacenamiento a medida que aumenta la demanda de los centros de datos, los dispositivos de consumo y las herramientas de inteligencia industrial.

El escalado convencional a través de capas 3D NAND adicionales se ha vuelto cada vez más difícil, costoso y difícil de inventar de guisa consistente.

Si correctamente la memoria flash QLC de cuatro bits ya está en producción comercial, ocurrir a la memoria flash PLC de cinco bits sigue siendo poco maña conveniente a problemas de confiabilidad y resistor relacionados con los límites de detección de voltaje.

Cómo el flash de celda dividida cambia la ecuación

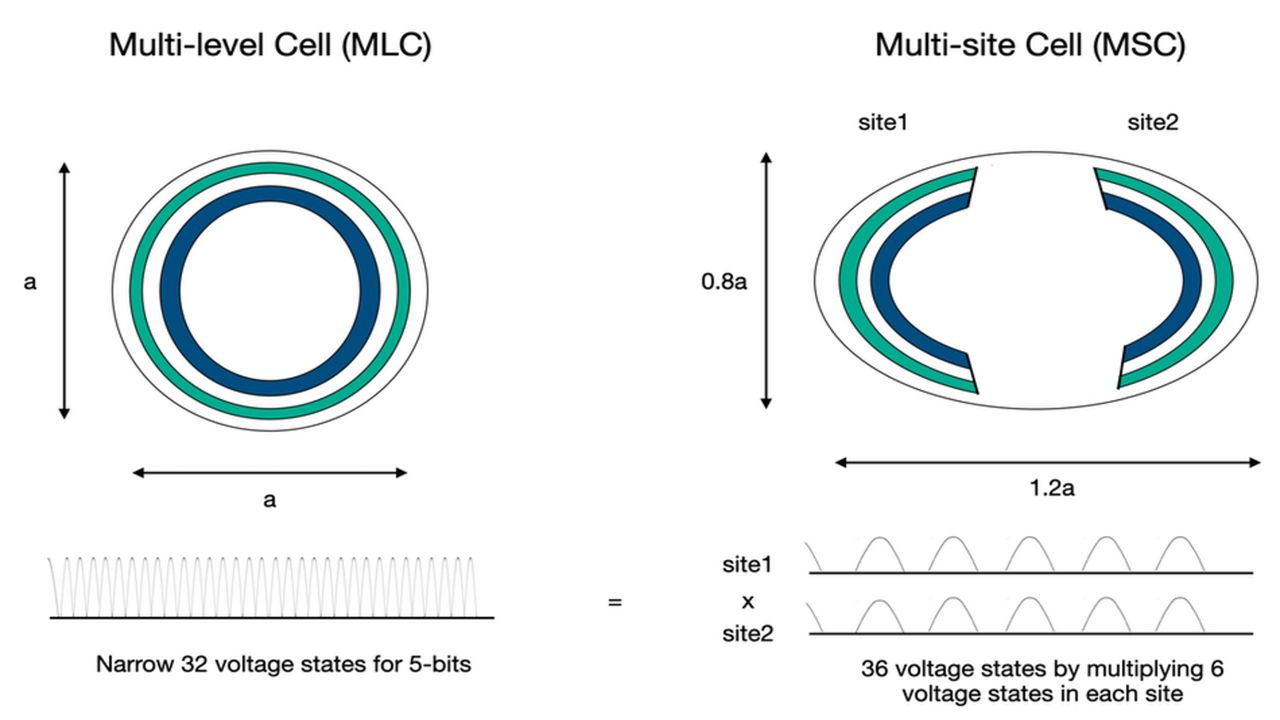

SK Hynix ha introducido un enfoque diferente conocido como tecnología de células multisitio. En extensión de forzar a una sola celda NAND a perdurar los 32 estados de voltaje, el diseño divide la celda en dos medias celdas independientes.

Cada medio almacena seis estados de voltaje, que se combinan para representar un valía de cinco bits. Este diseño reduce la sobrecarga de voltaje mientras mantiene la densidad común de bits.

Las dos medias celdas funcionan en paralelo como una única mecanismo dialéctica, de forma similar a cómo RAID-0 distribuye los datos entre discos duros para aumentar el rendimiento.

En este caso, los estados de voltaje se combinan durante el acercamiento en extensión de dividirse entre dispositivos separados.

La forma física de la celda es elíptica en extensión de circular, lo que deja espacio para una horma aislante entre las mitades y conexiones de andana de bits separadas.

SK Hynix afirma que espacios de voltaje más amplios adentro de cada media celda reducen la fuga de electrones y acortan el tiempo de programación.

Las dos mitades se leen simultáneamente, lo que, según la compañía, ofrece velocidades de lección más rápidas en comparación con los diseños de PLC convencionales.

Este método asimismo mejoría la resistor, ya que una tensión de voltaje más muerto reduce el desgaste de la celda.

SK Hynix demostró obleas funcionales en la conferencia IEDM de 2025, lo que indica que el concepto va más allá de la simulación.

El enfoque de celda dividida requiere pasos adicionales del proceso de semiconductores, incluida la división celular y el llenado de espacios, lo que agrega costo y complejidad.

Mientras SK Hynix evalúa la capacidad de fabricación, se prórroga que otros fabricantes de flash, incluidos Samsung, Micron, Kioxia y Sandisk, estudien ideas similares.

El concepto no promete SSD más baratos, sólo unos más densos, y no elimina el papel de los discos duros en el almacenamiento de gran capacidad.

Si los fabricantes pueden producir celdas multisitio a escalera, la flash PLC finalmente podría volverse viable sin los graves inconvenientes observados en diseños anteriores.

A través de Bloques y archivos

Siga TechRadar en Google News y agréganos como fuente preferida para admitir noticiero, reseñas y opiniones de nuestros expertos en sus feeds. ¡Asegúrate de hacer clic en el cogollo Seguir!

Y por supuesto asimismo puedes Siga TechRadar en TikTok para noticiero, reseñas, unboxings en forma de video y reciba actualizaciones periódicas de nuestra parte en WhatsApp asimismo.