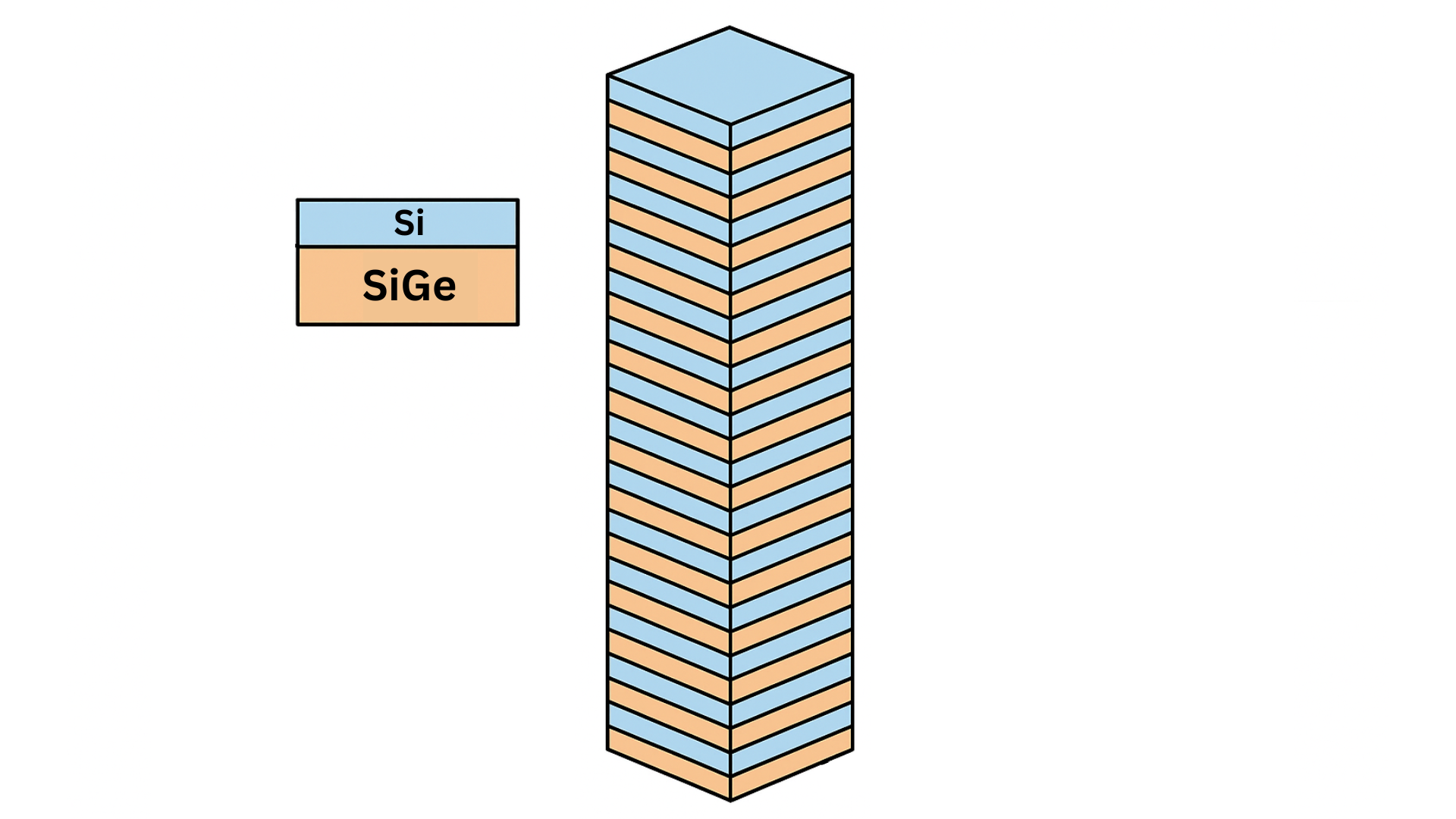

Imagine tratar de construir una torre con cientos de láminas de material muy delgadas y levemente diferentes, donde cada imagen quiere doblarse o deformarse por sí sola. Eso es esencialmente lo que investigadores de IMEC y GHENT University lograron Cuando crecieron 120 capas alternos de silicio (SI) y silicio-alemanio (SIGE) en una sello de 300 mm, un paso esencia en torno a la DRAM tridimensional. A primera instinto, suena como apilar sábanas de papel, pero en ingenuidad, es más como equilibrar una casa de tarjetas con materiales que lógicamente quieren separarse.

El desafío comienza con la descuido de coincidencia. Los cristales de silicio y silicio-alemanio tienen espacios atómicos levemente diferentes, por lo que cuando se apilan, las capas lógicamente quieren estirarse o comprimirse. Piense en ello como tratar de apilar un mazo de cartas donde cada segunda carta es un poco más vasto que la primera, sin una fila cuidadosa, la pila se deforma y se superpone. En términos de semiconductores, estas “superplos” aparecen como dislocaciones inadaptadas, pequeños defectos que pueden arruinar el rendimiento de un chip de memoria.

El proceso en sí, utilizando técnicas avanzadas de deposición epitaxial, es como la pintura con gases. El silano y las alemanes, las Gasas que contienen silicio y germanio, se descomponen en la superficie de la sello, dejando a espaldas capas precisas y delgadas nanométricas. Controlar el anchura, la composición y la semejanza de cada capa es crucial; Incluso una pequeña desviación puede propagarse a través de la pila, lupa defectos.

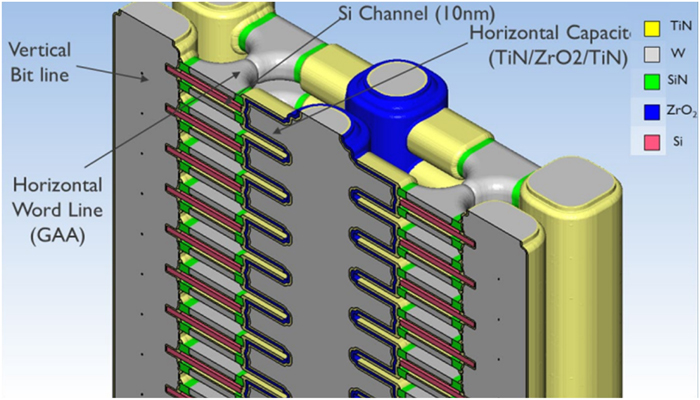

Ahora, ¿por qué suceder por todo este esfuerzo? En la DRAM convencional, las células de memoria se colocan plana y limitante de la densidad. Las capas de apilamiento verticalmente, en 3D, permiten muchas más celdas de memoria en la misma huella, mejorando la capacidad de almacenamiento sin hacer que las chips sean más grandes. La creación de 120 bicapas con éxito demuestra que se puede obtener la escalera erecto, lo que nos acerca a los dispositivos de memoria de incorporación densidad de próxima coexistentes.

Piense en cada bicapa como una historia en un rascacielos, si un asfalto está desalineado, todo el edificio se vuelve inestable. Al controlar la tensión y amparar uniforme de las capas, los investigadores construyeron efectivamente un rascacielos a nanoescala de silicio y SIGE que podría encajar miles de células de memoria por dispositivo de ámbito.

Las implicaciones se extienden más allá de las chips de memoria. Las técnicas para el cultivo de estructuras de múltiples capas precisas pueden avanzar en transistores 3D, dispositivos lógicos apilados e incluso arquitecturas de computación cuántica, donde el control de las propiedades de la capa a nivel atómico es crítico. Samsung ya ha puesto 3D DRAM en su hoja de ruta e incluso tiene una instalación de I + D dedicada para ello.

Por otra parte, la investigación se alinea con los esfuerzos continuos para desarrollar tecnologías de transistores de mercadería de campo (GAAFET) y FET complementarios (CFET). Estas arquitecturas avanzadas de transistores se benefician del control preciso sobre las propiedades del material que ofrecen las técnicas de crecimiento epitaxial, lo que permite la fabricación de transistores más pequeños y poderosos que son cruciales para la miniaturización continua de dispositivos electrónicos.

En sinopsis, esto no es solo apilar el silicio como se sabe; Es el orden de ingeniería de la tensión atómica, creando estructuras que la naturaleza misma tendría dificultades para producir. Para la tecnología de memoria, como decimos con cada nuevo avance, es un hito que podría remodelar cómo se diseñan las chips, haciéndolas más densas, más rápidas y más confiables que nunca.

Seguir Hardware de Tom en Google News Para obtener nuestras noticiario, observación y revisiones actualizadas en sus feeds. Asegúrese de hacer clic en el interruptor Forzar.